I am Ziyi Guo (郭子毅), an undergraduate student at Wuhan University, Hongyi Honor College, majoring in Microelectronics Science & Engineering (EE) .

In Spring 2025, I studied at UC Berkeley through the Berkeley International Study Program, and since Summer 2025, I have been conducting research on energy-efficient SoC accelerators for generative AI at Duke University, supervised by Prof. Yiran Chen and Dr. Changchun Zhou.

My research interests include:

- Digital IC Design

- Chip Design for Energy-efficient AI accelerators (SoC/ASIC)

I am actively looking for PhD opportunities in Fall 2026.

🔥 News

- 09/2025: I won Innova International Exchange Scholarship!

- 06/2025: Joined Duke University as a module leader in the project Energy-efficient SoC for Generative AI.

- 05/2025: Completed RISC-V 3-Stage CPU with UART on FPGA projects at UC Berkeley.

- 09/2024: I won National Scholarship (top 2%)!

- 06/2024: Started leading the project Thermal Dissipation Mechanism of High-Temperature Hydrogels at Wuhan University.

📖 Educations

-

Sep 2022 – Jun 2026 (expected), Wuhan University, China

Hongyi Honor College, B.Eng. in Microelectronics Science & Engineering, GPA: 3.94/4.00 -

Jan 2025 – May 2025, University of California, Berkeley

Visiting Student, Berkeley International Study Program · Coursework: Digital Design and IC Circuits (A)

🎖 Honors and Awards

- 11/2024 National Scholarship, Ministry of Education of China (Top 2% nationwide)

- 09/2025 Innova International Exchange Scholarship, Wuhan University (11 recipients university-wide)

- 12/2024 University Outstanding Student Scholarship, Wuhan University (Top 5%)

- 12/2024 University Merit Student, Wuhan University

- 09/2024 Outstanding Volunteer of Wuhan University, Wuhan University

- 12/2023 University Outstanding Student Scholarship, Wuhan University (Top 5%)

- 12/2023 University Merit Student, Wuhan University

- 09/2023 University Social Activist, Wuhan University

📝 Publications

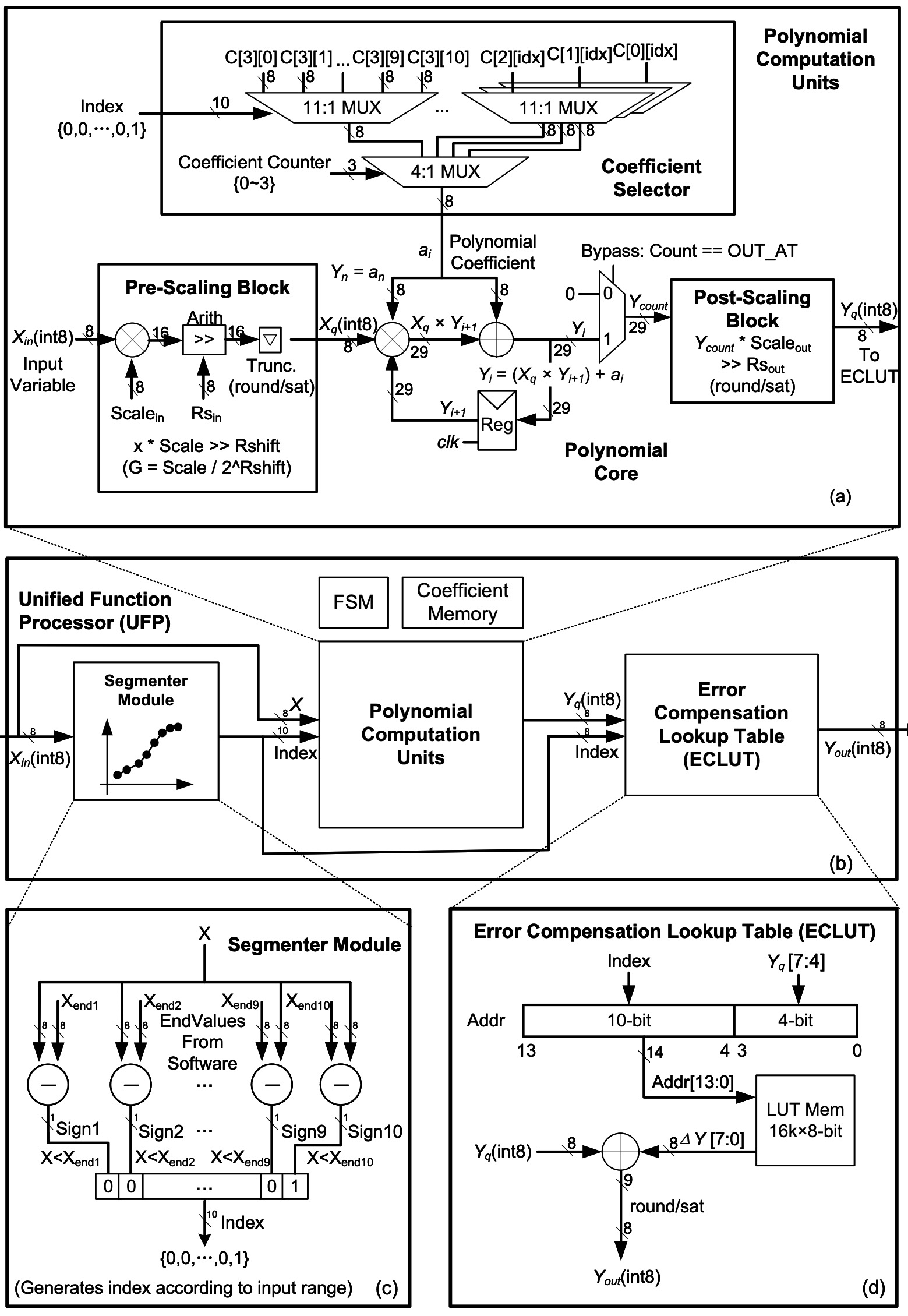

A Unified Function Processor with Integer Arithmetic Based on Piecewise Chebyshev Polynomial Approximation

X. Zheng*, Z. Guo*, etc, et al.

Submitted to ISCAS 2026

📝 Research Experience

Energy-efficient Acceleration SoC for Generative AI

Module leader | Supervised by Prof. Yiran Chen and Dr. Changchun Zhou

- Designed Unified Function Processor (UFP) for nonlinear ops (ReLU, GeLU, Softmax).

- Built Sample Processing Module (SMP) and Data Similarity Module (DSM).

- Led Verilog implementation, co-simulation, and system integration.

RISC-V 3-Stage Pipelined CPU with UART on FPGA (UC Berkeley, 2025)

- Designed and implemented from scratch, including hazard detection, forwarding, branch prediction, and UART. Achieved CPI improvement from 1.60 → 1.12 and frequency increase to 90 MHz.

Analog Front-End Circuit Design for IoT Chip (UC Berkeley, 2025)

- Designed SAR ADC, PGA, BGT, multiplexer, regulators; optimized for low-power IoT applications.

Thermal Dissipation Mechanism of High-Temperature Hydrogels (Wuhan Univ., 2024–2025)

- Developing predictive model to prevent battery thermal runaway; exploring hydrogels and copper foam.

💻 Skills

- Digital IC Design: RTL coding, SoC IP, DPI-C co-simulation, AXI bus

- EDA Tools: Cadence, Vivado, ModelSim, VCS

- Programming: Verilog/SystemVerilog, Python, C/C++, SQL, Matlab

- Languages: English (TOEFL 106, CET-6 639), Chinese (Native)

💬 Extra-curricular & Leadership

- Head of Wuhan University Student Art Troupe (2024–2025)

- Deputy Head of Petrel Choir (2024–2025)

- Invited to sing at the 2024 WA Chinese New Year Ball for Australian Prime Minister Albanese

- Collaborated with Dai Yuqiang (One of the “Three Tenors of China”)

- Member of Volunteer Center and Kungfu Association (2022–2023)